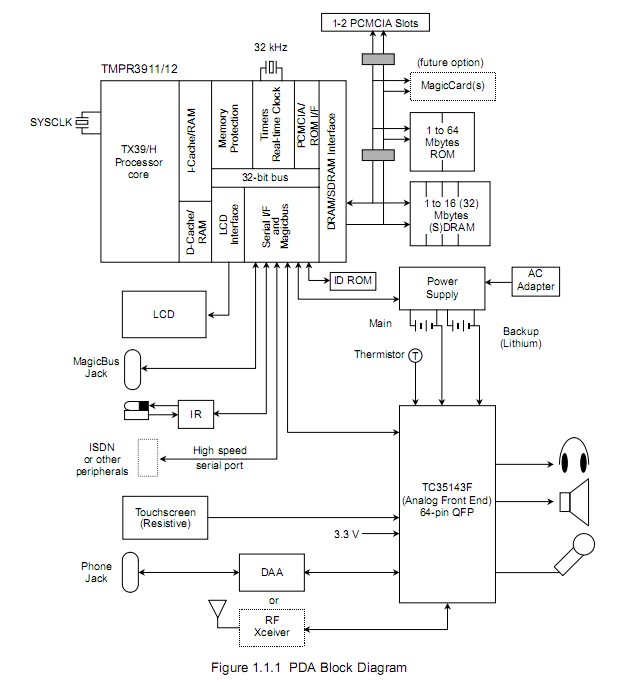

Product Summary

The TMPR3912AUG-92 is a single-chip, integrated digital ASSP for the Personal Digital Assistants (PDA). Figure 1.1.1 shows a block diagram of the overall PDA system. The TMPR3912AUG-92 consists of the PDA system support logic, integrated with an embedded TX39/H Processor core designed by TOSHIBA. The TMPR3912AUG-92 consists of a TX39/H Processor core with 4 Kbytes of instruction cache memory and 1Kbyte of data cache memory, plus integrated functions for interfacing to numerous system components and external I/O modules. The TMPR3912AUG-92 also contains multiple DMA channels and a high-performance and flexible Bus Interface Unit (BIU) for providing an efficient means for transferring data between external system memory, cache memory, the Processor core, and external I/O modules.

Parametrics

TMPR3912AUG-92 absolute maximum ratings: (1)Supply voltage (I/O) VDD: VSS - 0.5 to 4.5 V; (2)Supply voltage (Internal Logic) VDDL: VSS - 0.5 to VDDH V; (3)Input voltage VIN VSS: - 0.5 to VDDH + 0.5 V; (4)Storage temperature TSTG: -55 to 125 ℃; (5)Maximum dissipation (Ta = 70℃) PD: 1W.

Features

TMPR3912AUG-92 features: (1)Entire TMPR3911/12 operation is 3.3 V (in case of TMPR3911BU/BXB, I/O: 3.3 V, internal: 2.6 V); (2)Real-time clock based on 32.768 kHz reference; (3)Processor core clock stop state for low standby current power-down modes for individual internal peripheral modules; (4)High level of integration on a single chip, small board space, low pin count, low power, and high performance.

Diagrams

|

TMPR28051 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TMPR28051 STS-1 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TMPR3911 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TMPR3912AU |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TMPR3912XB-75 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TMPR3916 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)